http://wiki.csie.ncku.edu.tw/embedded/I2C

http://www.ti.com/lit/an/slva704/slva704.pdf

I2C

- 連線基本上是wired-and,有一個裝置拉low 則整個bus都low

- 基本上1 master -> n slave

- 但可有多master

- 基本上master在有資料傳輸時會等待

- 若兩個master很剛好同時要運作,wired-and 特性會讓其中一個master發現到有人同時在傳而停止傳輸

- 若 Master 1 欲將 SDA logic 拉高,最後卻 SDA logic 為低,代表仲裁輸了,該 master 立即停止動作。

- 若同時起始傳輸,與較小slave address 溝通的master會拿到bus(因為與較大slave address溝通的master會在address內的某個bit寫1,但bus卻仍為0)

- 同理,若slave address 相同,則write 的master 拿到bus(因為write bit為0, read 的master 發現設1但讀出為0)

- 若兩個master 皆為Read, 則沒差,

- 若兩個master 皆為write, 則看誰比較先遇到寫1時另一個master寫0

- 輸掉的 master 寧可先放棄 (Back Off) 等候,到看見停止狀態的出現才開始傳送。

- Serial, 8-bit oriented, bidirectional data transfers

- slave address:

- 7bit, 保留16個,故最多只能跟112個節點通訊

- 1byte

- addr bit 6~0 + R/W bit

- 10bit, 分2byte傳輸, ,address 開頭固定為11110

- byte1: 11110 + bit9 bit8 + R/W

- byte2: bit 7~0

- bus

- speed:

- 低速 10Kbit/s

- 標準 100Kbit/s standard-mode

- 快速 400Kbit/s fast-mode

- 快速+ 1Mbit/s fast-mode plus\

- 高速 3.4Mbit/s high-speed mode

- 超快速: 5Mbps ultra fast-mode(uni-direction)

- 2 pin, 需要pull high,

- SDA: data

- SCL: clock

- terminology

- Transmitter : the device which sends data to the bus

- Receiver : the device which receives data from the bus

- Master : the device which initiates a transfer, generates clock signals and terminates a transfer

- Slave : the device addressed by a master

- read/write整體流程

- write

- master:

- START

- send slave address(7bit) + 0(1bit, r=1, w=0)

- slave:

- 回ACK(SCL=high 時將SDA 拉low)

- master:

- send register address(8b)

- slave:

- ACK

- master send new register value

- slave ACK

- 這兩步可repeat, 代表接著寫下一個register

- 結束後master 送STOP

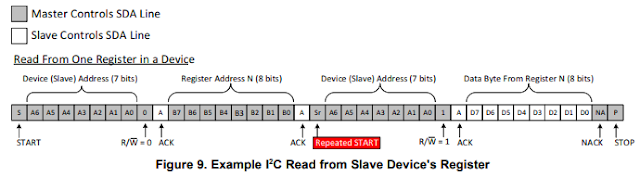

- read

- master

- START

- send slave address(7bit) + 0(1bit, r=1, w=0) 注意是write, 因為master 要先寫register address給slave

- slave

- ACK

- master:

- send register address(8bit)

- slave:

- ACK

- Master

- START again

- send slave address(7bit) + 1(1bit, r=1, w=0) slave已經知道register address, 這邊才跟slave 說要讀

- slave

- ACK

- slave send register value

- master NACK

- master STOP

- 資料傳輸

- 一次傳1 byte, 然後收ack,若無ack則代表出問題,停止傳輸,丟出STOP

- data transmit

- START bit

- SCL high, SDA high->low

- DATA

- SCL high, SDA stable

- SDA 變動時只能在SCL 為low的時候

- STOP bit

- SCL high, SDA low->high

擷取自TI 文件(http://www.ti.com/lit/an/slva704/slva704.pdf):

沒有留言:

張貼留言